# SCLT3-8BQ7

Datasheet - production data

## High speed digital input current limiter with digital filter

## Features

- 8 inputs 8-bit SPI output

- High side input with common ground

- 5 V Voltage regulator

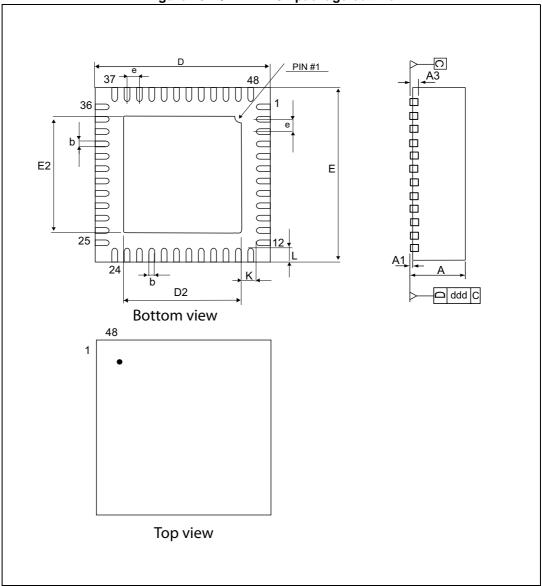

- Package: QFN 7x7 48L

- 30 V reverse polarity capable

- Adjustable current limiters

- LED output for visual status

- Optional: 16-bit mode with parity check, temperature and voltage alarms

- Daisy chain capable

- Input digital filter with adjustable delay: 20 µs to 3 ms

- Power dissipation: 78 mW per channel

## Complies with following standards:

- IEC61000-4-2:

- ±8 kV contact discharge

- ±15 kV air discharge

- IEC61000-4-4:

- ±4 kV

- IEC61000-4-5:

- Input: ±1 kV

- Power supply: ±2.5 kV

## Application

- Programmable logic controller and remote input modules

- High speed protected termination for digital input with serialized SPI output

- IEC61131-2 type 1, 2 and 3

- Compliant with EN60947-5-2

## Benefits

- Simplified design due to

- Built-in over voltage robustness and immune data transfer

- Compliance with sensors and PLC's standards

- Space saving in cost effective solution with

- Integrated QFN 7x7 package

- SPI output reducing opto-couplers quantity

- Energy efficient solution

- Energy-less input LED visual status powered by inputs current

- Low overall dissipation versus discrete

## Description

The SCLT3-8BQ7 provides an 8-line protected digital input termination with serialized state transfer. This device enhances the I/O module density by cutting the dissipation (78 mW per input) and reducing the count of opto-transistors. An adjustable digital filter and an LED driver are embedded in each type 3 input section. Its 2 MHz SPI peripheral output serializes the input state transfer to the I/O module controller.

#### November 2015

DocID027845 Rev 2

This is information on a product in full production.

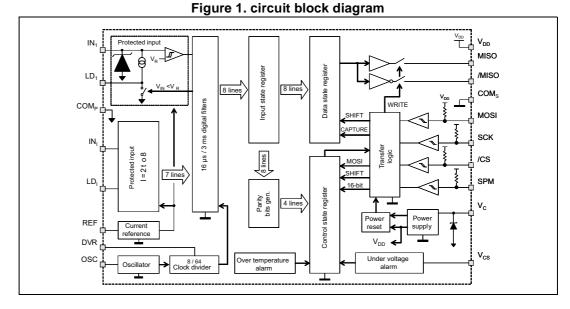

1 Circuit block diagram

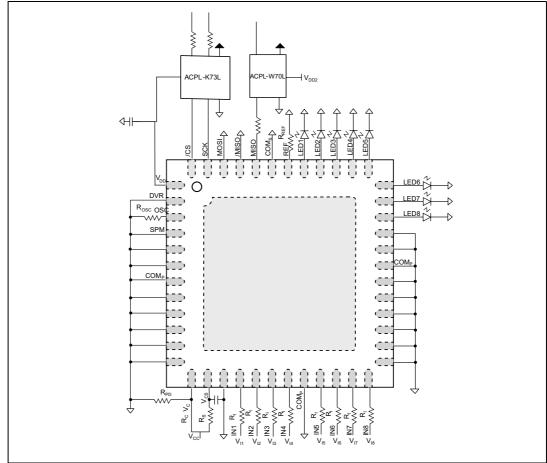

### Figure 2. Basic application schematic

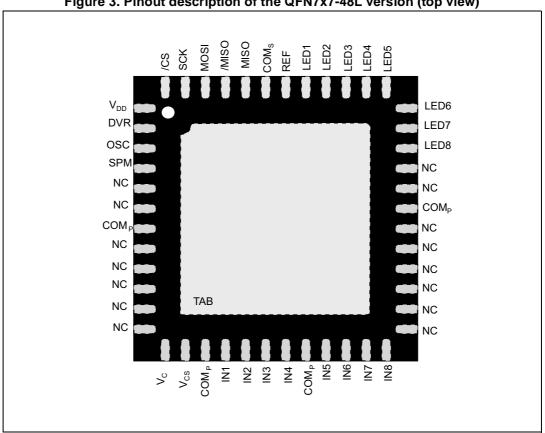

# 1.1 I/O pin description

|                  | _            | Table 1. I/O pin descriptions                                                       |                                                           |

|------------------|--------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Name             | Туре         | Description                                                                         | Pin #                                                     |

| INI              | Power input  | Logic input with current limitation, I = 1 to 8                                     | 16, 17, 18, 19,<br>21, 22, 23, 24                         |

| LD               | Power output | LED output driver with current regulation, I = 1 to 8                               | 34, 35, 36, 37,<br>38, 39, 40, 41                         |

| V <sub>C</sub>   | Power input  | 24 V sensor power supply                                                            | 13                                                        |

| V <sub>CS</sub>  | Signal input | 24 V sensor power supply sensing input                                              | 14                                                        |

| COM <sub>P</sub> | Ground       | Power ground of power sensor supply                                                 | 7, 15, 20, 31                                             |

| V <sub>DD</sub>  | Power output | 5 V logic power supply                                                              | 1                                                         |

| COM <sub>S</sub> | Ground       | Signal ground of logic / output section                                             | 43                                                        |

| REF              | Signal input | Input current limiter reference setting                                             | 42                                                        |

| SPM              | Signal input | SPI shift register length selector<br>-SPM to GND> 16 bits<br>-SPM to VDD> 8 bits   | 4                                                         |

| /CS              | Logic input  | SPI chip Select signal                                                              | 48                                                        |

| SCK              | Logic input  | SPI serial clock signal                                                             | 47                                                        |

| MOSI             | Logic input  | SPI serial data input signal                                                        | 46                                                        |

| DVR              | Logic input  | Divider ratio selector of the digital input filters (8 or 64 steps)                 | 2                                                         |

| OSC              | Signal input | Delay setting of the digital input filters                                          | 3                                                         |

| MISO             | Logic output | SPI serial data output signal                                                       | 44                                                        |

| /MISO            | Logic output | Inverting SPI serial data output signal                                             | 45                                                        |

| TAB              | Substrate    | Exposed pad: connected to die substrate, to be connected to $\text{COM}_{\text{P}}$ | ТАВ                                                       |

| NC               |              | Not connected (or to be connected to $\text{COM}_{\text{P}}$ )                      | 5, 6, 8, 9, 10, 11, 12, 25, 26,<br>27, 28, 29, 30, 32, 33 |

Table 1. I/O pin descriptions

Figure 3. Pinout description of the QFN7x7-48L version (top view)

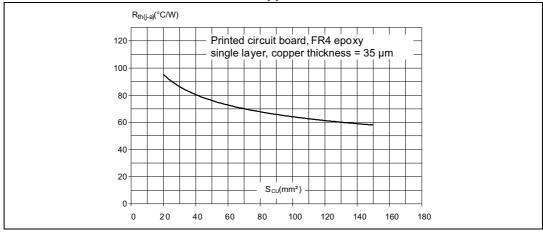

The package is the QFN7x7-48L exposed pad that improves ground cooling transfer of input dissipation to the printed board.

# 2 Characteristic information

|                  |                    |                                        | lin radings                     |            |      |

|------------------|--------------------|----------------------------------------|---------------------------------|------------|------|

| Symbol           | Pin                | Parameter name                         | Conditions                      | Value      | Unit |

| V <sub>CC</sub>  | V <sub>c</sub>     | Bus power supply DC voltage            | 500 Ω < R <sub>c</sub> < 2.2 kΩ | -0.3 to 35 | V    |

| V <sub>C</sub>   | Vc                 | SCLT3-8BQ7 power supply voltage        | R <sub>c</sub> = 0 kΩ           | -0.3 to 30 | V    |

| I <sub>CC</sub>  | V <sub>c</sub>     | Maximum bus power supply current       |                                 | 15         | mA   |

| V <sub>CS</sub>  | V <sub>CS</sub>    | Sensing bus power supply voltage       | ensing bus power supply voltage |            | V    |

| I <sub>DD</sub>  | V <sub>DD</sub>    | Maximum output power supply current    | R <sub>c</sub> = 500 Ω          | 12         | mA   |

| VI               | INI                | Input steady state voltage, I = 1 to 8 | R <sub>I</sub> = 2.2 kΩ         | -30 to 35  | V    |

| I <sub>IN</sub>  | INI                | Input forward current range            |                                 | -20 to 10  | mA   |

| I <sub>OSC</sub> | OSC                | Maximum sourced oscillator current     |                                 | 120        | μA   |

| LVI              | SCK<br>/CS<br>MOSI | Logic input voltage                    |                                 | -0.3 to 6  | V    |

| T <sub>stg</sub> | All                | Storage temperature range              |                                 | -40 to 150 | °C   |

| T <sub>amb</sub> | All                | Ambient temperature range              |                                 | -40 to 105 | °C   |

#### Table 2. Absolute maximum ratings

| Symbol               | Pin                                 | Parameter name                         | Conditions                                                               | Value                   | Unit |  |  |

|----------------------|-------------------------------------|----------------------------------------|--------------------------------------------------------------------------|-------------------------|------|--|--|

| V <sub>CC</sub>      | V <sub>c</sub>                      | Bus power supply steady state voltage  | R <sub>c</sub> > 500 Ω                                                   | 15 to 35 <sup>(1)</sup> | V    |  |  |

| V <sub>DD</sub>      | V <sub>DD</sub>                     | Internal logic power supply voltage    |                                                                          | 5                       | V    |  |  |

| I <sub>DD</sub>      | V <sub>DD</sub>                     | Internal logic power supply voltage    | $R_c > 500 \; \Omega$                                                    | 10                      | mA   |  |  |

| VI                   | IN                                  | Input repetitive steady state voltage  | nput repetitive steady state voltage $R_{I} = 2.2 \text{ k}\Omega^{(2)}$ |                         |      |  |  |

| V <sub>LD</sub>      | LD                                  | Maximum LED output voltage, I = 1 to 8 | faximum LED output voltage, I = 1 to 8                                   |                         |      |  |  |

| F <sub>IN MAX</sub>  | IN                                  | Maximum single input frequency         | 8-bit mode                                                               | 20                      | kHz  |  |  |

| F <sub>SCK MAX</sub> |                                     | Maximum SPI clock frequency            |                                                                          | 0.1 to 2                | MHz  |  |  |

| R <sub>OSC</sub>     | OSC                                 | Filter oscillator resistance range     |                                                                          | 15 k to 1.5 M           | Ω    |  |  |

| LV                   | SCK<br>/CS<br>MOSI<br>MISO<br>/MISO | Logic input/output voltages            |                                                                          | 0 to 5.5                | V    |  |  |

|                      |                                     |                                        | V <sub>CC</sub> ≤30 V                                                    | -40 to 85               |      |  |  |

| T <sub>amb</sub>     | ALL                                 | Operating ambient temperature range    | V <sub>CC</sub> ≤ 24 V<br>R <sub>th(j-a)</sub> = 70 °C/W                 | -40 to 105              | °C   |  |  |

| Тj                   |                                     | Operating junction temperature range   |                                                                          | -40 to 150              | °C   |  |  |

| Table 3. | Operating | conditions |

|----------|-----------|------------|

|----------|-----------|------------|

1. 32 V in DC; 35V during 0.5 s max

2.  $V_I = V_{IN} + R_I \times I_{IN}$

| Symbol           | Pin        | Name                   | Conditions                                               | Min.                 | Тур.                  | Max.                 | Unit |

|------------------|------------|------------------------|----------------------------------------------------------|----------------------|-----------------------|----------------------|------|

| Input Curr       | ent limita | tion                   | -                                                        |                      |                       |                      |      |

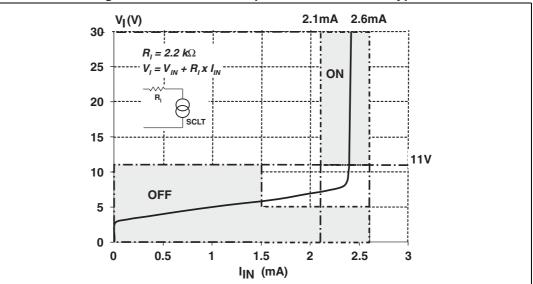

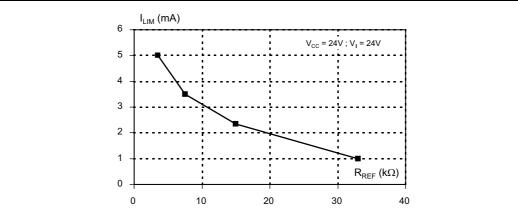

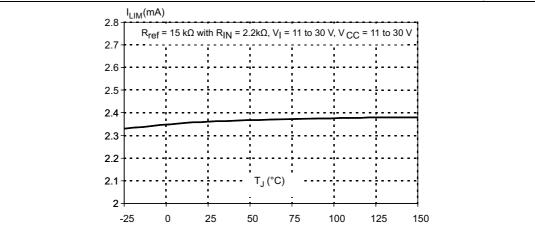

| I <sub>LIM</sub> | IN         | Input limiting current | V <sub>IN</sub> = 5.5 to 26 V<br>R <sub>I</sub> = 2.2 kΩ | 2.1                  | 2.35                  | 2.6                  | mA   |

| I <sub>ON</sub>  | LD         | On state LED current   | V <sub>I</sub> = 11 V                                    | 2                    |                       |                      | mA   |

| Input digit      | al filter  |                        |                                                          | <u> </u>             |                       |                      |      |

| т                | OSC        | C Oscillator pariad    | R <sub>OSC</sub> = 51 kΩ                                 | 1.13                 |                       | 1.37                 | μs   |

| T <sub>OSC</sub> | 030        | Oscillator period      | R <sub>OSC</sub> = 1200 kΩ                               | 20                   |                       | 28                   | μs   |

| R <sub>OSC</sub> | OSC        | Oscillator resistance  |                                                          | 51                   |                       | 1200                 | kΩ   |

|                  |            | CKE pariad             | DVR = V <sub>DD</sub>                                    | 6                    | 64 x T <sub>OSC</sub> |                      |      |

| t <sub>CKF</sub> |            | CKF period             | DVR = COM <sub>s</sub>                                   |                      | 8 x T <sub>OSC</sub>  |                      |      |

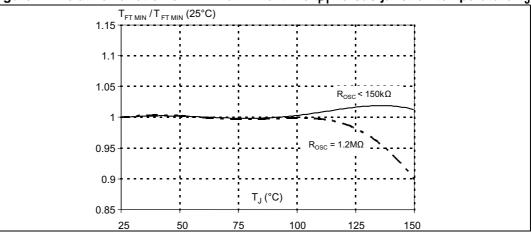

| t <sub>FT</sub>  | IN         | Filtering time         |                                                          | 2 x t <sub>CKF</sub> |                       | 3 x t <sub>CKF</sub> |      |

| Symbol                            | Pin                | Name                       | Conditions                                                        | Min. | Тур. | Max. | Unit |

|-----------------------------------|--------------------|----------------------------|-------------------------------------------------------------------|------|------|------|------|

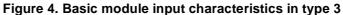

| F <sub>CK</sub>                   | SCK                | Clock frequency            |                                                                   |      |      | 2    | MHz  |

| т <sub>s</sub>                    | MOSI               | Data setup time            | MOSI toggling to SCK rising                                       | 25   |      |      | ns   |

| т <sub>D</sub>                    | MISO               | Write out propagation time | on time SCK falling to MISO<br>toggling, C <sub>OUT</sub> = 10 pF |      | 50   | ns   |      |

| T <sub>LD</sub>                   | SCK                | Enable lead time           | /CS falling to SCK rising                                         | 80   |      |      | ns   |

| T <sub>HC</sub>                   | SCK                | Clock hold time            | SCK falling to /CS rising                                         | 160  |      |      | ns   |

| T <sub>DT</sub>                   | /CS                | Transfer delay time        | /CS rising to /CS falling                                         |      |      | 150  | ns   |

| т <sub>н</sub>                    | MOSI               | Data hold time             | SCK rising to MOSI toggling                                       | 25   |      |      | ns   |

| T <sub>DIS</sub>                  | MISO               | Data output disable time   | /CS rising to MISO disabled                                       |      |      | 200  | ns   |

| LV <sub>IH</sub>                  | MOSI<br>SCK<br>/CS | Logic input high voltage   | Share of V <sub>DD</sub>                                          |      |      | 70   | %    |

| LV <sub>IL</sub>                  |                    | Logic input low voltage    | Share of V <sub>DD</sub>                                          | 30   |      |      | %    |

| LV <sub>OH</sub>                  | /MISO<br>MISO      | Logic output high voltage  | I <sub>OH</sub> = 3mA                                             | 4    | 4.75 |      | V    |

| LV <sub>OL</sub>                  |                    | Logic output low voltage   | I <sub>OL</sub> = 3mA                                             |      | 0.25 | 1    | V    |

| T <sub>RO</sub> , T <sub>FO</sub> | MISO<br>/MISO      | MISO signal fall/rise time | I <sub>MISO</sub> = 3mA                                           |      | 20   |      | ns   |

| T <sub>A</sub>                    | MISO               | Output access time         | /CS falling to MISO toggling                                      |      | 40   | 80   | ns   |

| DuCy                              | SCK                | Clock duty cycle           |                                                                   | 25   |      | 75   | %    |

# Table 5. SPI electrical characteristics ( $T_j = 25 \degree C$ , $V_{CC} = 24 \lor V$ , $V_{DD} = 5 \lor V$ respect to COM ground pin;unless otherwise specified)

### Figure 5. Time diagram

| Symbol           | Pin             | Parameter name <sup>(1)</sup>                                  | Value   | Unit |  |  |  |  |

|------------------|-----------------|----------------------------------------------------------------|---------|------|--|--|--|--|

| V <sub>PPB</sub> | VI              | Peak pulse voltage burst, IEC61000-4-4 <sup>(2)</sup>          | 4       | KV   |  |  |  |  |

| V <sub>PP</sub>  | VI              | Peak pulse voltage surge, IEC61000-4-5                         | 1       | kV   |  |  |  |  |

| V <sub>PP</sub>  | V <sub>CC</sub> | Peak pulse voltage surge, IEC61000-4-5                         | 2.5     | kV   |  |  |  |  |

| V <sub>ESD</sub> | V <sub>IN</sub> | ESD protection, IEC 61000-4-2, per input<br>– air<br>– contact | 15<br>8 | kV   |  |  |  |  |

### Table 6. Electromagnetic compatibility ratings

1. Test set-up, see application *Figure* 2.

2. See AN3031.

## 3 Functional description

# 3.1 Operation of the SCLT3-8BQ7 with the SPI bus ( $C_{POL} = 0$ , $C_{PHA} = 0$ )

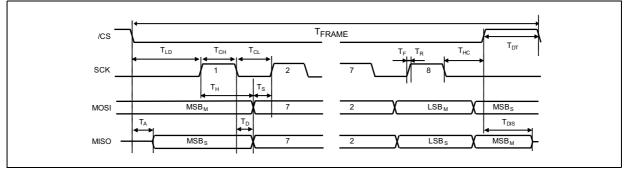

The SPI bus master controller manages the data transfer with the chip select signal /CS and controls the data shift in the register with the clock SCK signal.

Figure 6. Serial data format frame

The transfer of the SCLT3-8BQ7 input states in the SPI registers starts when the Chip Select /CS signal falls and ends when this /CS is rising back.

The transfer of data out of the SCLT3-8BQ7 slave MISO output starts immediately when the chip select /CS goes low.

Then, the input MOSI is captured and presented to the shift register on each rising edge of the clock SCK. And the data are shifted in this register on each falling edge of the serial clock SCK, the data bits being written on the output MISO with the most significant bit first.

## 3.1.1 The serial data Input MOSI

This input signal MOSI is used to shift external data bits into the SCLT3-8BQ7 register from the most significant MSB bit to the lower significant one LSB. The data bits are captured by the SCLT3-8BQ7 on the rising edge of the serial clock signal SCK.

## 3.2 The input digital filter

Depending on the biasing of the SPM pin, the data frame is 8-bits or 16-bits.

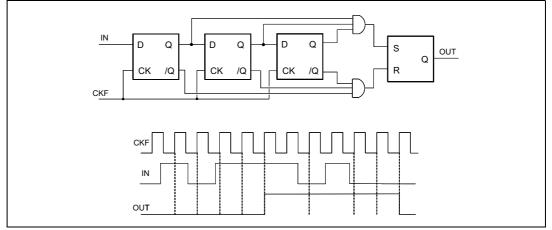

A digital filter is implemented between the input state comparator and the input state register. It consists of a 2-step sampling circuit that is controlled by an oscillator as shown on *Figure 7*.

The filtering time  $t_{FT}$  is set by the external oscillator resistor and is a function of the oscillator period  $t_{CKF}$ :

- 2 x t<sub>CKF</sub> < t<sub>FT</sub> < 3 x t<sub>CKF</sub>

- t<sub>CKF</sub> = Divider ratio x t<sub>OSC</sub> (R<sub>OSC</sub>)

This period can be adjusted between 20  $\mu s$  and 3000  $\mu s$  as shown on Table 7.

| Input speed                      | Fast             |                  | ut speed Fast   |                 | Medium | Slow |

|----------------------------------|------------------|------------------|-----------------|-----------------|--------|------|

| Input frequency (kHz)            | 60               | 20               | 5               | 0.3             |        |      |

| Min. filter time $t_{FT}$ (µs)   | 20               | 50               | 230             | 3000            |        |      |

| OSC resistance (kΩ)              | 51               | 150              | 82              | 1300            |        |      |

| CKF period t <sub>CKF</sub> (µs) | 10               | 25               | 115             | 1500            |        |      |

| DVR connection                   | COM <sub>S</sub> | COM <sub>S</sub> | V <sub>DD</sub> | V <sub>DD</sub> |        |      |

| Divider ratio                    | 8                | 8                | 64              | 64              |        |      |

Being placed in the front end of the module, this filter increases the transient immunity of the SCLT and its SPI logic circuitry. It also simplifies the input management software task of the ASIC controller.

Figure 7. Two step digital filter placed after the analog section of the logic input

## 3.3 The SPI data transfer operation

## 3.3.1 The SPI data frame

Depending on the biasing of the SPM pin, the data frame is 8-bits or 16-bits. The selected structure of the SPI is a 16-bit word in order to be able to implement the input state data and some control bits such as the UVA alarm, the 4 checksum bits and the two low & high state stop bits.

## 3.3.2 The SPI data transfer

The SCLT3-8BQ7 transfers its 16 data bits through the SPI within one chip select Hi-Lo-Hi sequence. So, this length defines the minimum length that the shift register of the SPI master controller is able to capture: 16 bits.

The *Table 8* shows the 16-bit mode way the data are transferred starting from the data bits, the control bits and ending by a stop bit.

| Bit #   | LSB  | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 | Bit 6 | Bit 7 |

|---------|------|-------|-------|-------|-------|-------|-------|-------|

| Control | High | Low   | PC4   | PC3   | PC2   | PC1   | /OTA  | /UVA  |

Table 8. SPI data transfer organization versus CLT input states with SPM = 0

Last out

| Bit # | Bit 8 | Bit 9 | Bit 10 | Bit 11 | Bit 12 | Bit 13 | Bit 14 | MSB  |

|-------|-------|-------|--------|--------|--------|--------|--------|------|

| Data  | IN 1  | IN 2  | IN 3   | IN 4   | IN 5   | IN 6   | IN 7   | IN 8 |

First out

## 3.4 Control bit signals of the SPI transferred data frame

### 3.4.1 The power bus voltage monitoring

The UVA circuit generates the alarm /UVA that is active low when the power bus voltage is lower than the activation threshold  $V_{CON}$ , 17 V typical, and it is disabled high when the power bus voltage rises above the threshold  $V_{COFF}$ , 18 V typical.

## 3.4.2 The over temperature alarm

The alarm signal /OTA is enabled, low state active, when the junction temperature is higher than the activation threshold  $T_{ON}$ , 150 °C typical, and it is disabled when the junction temperature falls below the threshold  $T_{OFF}$ , 140°C typical.

## 3.4.3 The parity checksum bits calculation and transfer

The aim of the parity checksum bit is to detect one error in the transferred SPI word. Several parity checksum bits are generated and transmitted through the SPI on the control bit #2 to #5.

In order to calculate parity bit, "exclusive NOR" operations are performed as follow:

|     |     |     |     | · · · · · · · · · · · · · · · · · · · |     |     |      |

|-----|-----|-----|-----|---------------------------------------|-----|-----|------|

| HN8 | IN7 | IN6 | IN5 | IN4                                   | IN3 | IN2 | 1111 |

|     | 0   | 0   | 1   | Y                                     | 0   | 0   | 1    |

|     |     | +   |     |                                       |     |     |      |

|     |     | PC1 | PC2 | PC3                                   | PC4 |     |      |

|     |     | 1   | 1   | 1                                     | 1   |     |      |

#### Table 9. SCLT3-8BQ7 parity bit calculation example

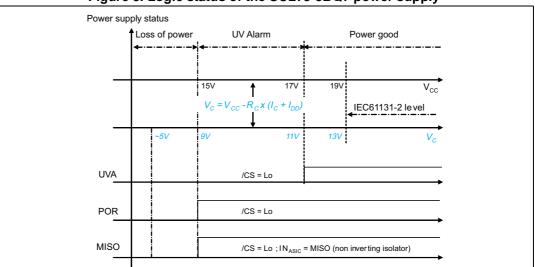

## 3.5 Loss of V<sub>CC</sub> power supply

The operation of the SCLT3-8BQ7 is extended below the levels required in the IEC 61131-2 standard to allow the implementation of the under voltage alarm UVA as described the SPI control bit section.

If there is no more power feeding on the  $V_{CC}$  input, the SCLT3-8BQ7 chip goes to sleep mode, and the MISO output is forced in low state during SPI transfer attempt. The last SPI control data bit is a stop bit placed normally in high state all time: the loss of power supply is detected by checking its state: if low, the output is disabled by the internal power reset POR.

This POR signal is active in low state when  $V_C$  is less than 9V or the internal power supply  $V_{DD}$  is less than 3.25 V.

| POR | /CS | MISO | /MISO | SPI status                            |

|-----|-----|------|-------|---------------------------------------|

| 1   | 1   | Z    | Z     | Normal with no communication          |

| 1   | 0   | 1    | 0     | Normal with communication             |

| 1   | 0   | 0    | 1     | Normal with communication             |

| 0   | 1   | Z    | Z     | Power loss with no communication      |

| 0   | 0   | 0    | 1     | Power loss with communication attempt |

| Table 10. Logic state of the SPI output versus the power loss signal POR and the SPI |

|--------------------------------------------------------------------------------------|

| chip select /CS                                                                      |

Figure 8. Logic status of the SCLT3-8BQ7 power supply

Figure 11. Relative variation of minimum filter time  $t_{FT}$  versus junction temperature  $T_J$

Figure 12. Variation of junction to ambient thermal resistance R<sub>th(j-a)</sub> versus printed circuit board copper surface SCU

# 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

## 4.1 QFN7x7-48L package information

Figure 13. QFN7x7-48L package outline

|      |            |             |      | je meename            |        |        |  |  |

|------|------------|-------------|------|-----------------------|--------|--------|--|--|

|      | Dimensions |             |      |                       |        |        |  |  |

| Ref. |            | Millimeters |      | Inches <sup>(1)</sup> |        |        |  |  |

|      | Min.       | Тур.        | Max. | Min.                  | Тур.   | Max.   |  |  |

| А    | 0.80       | 0.90        | 1.00 | 0.0315                | 0.0354 | 0.0394 |  |  |

| A1   |            | 0.02        | 0.05 |                       | 0.0008 | 0.0020 |  |  |

| A3   |            | 0.203       |      |                       | 0.008  |        |  |  |

| b    | 0.18       | 0.25        | 0.30 | 0.0071                | 0.0100 | 0.0118 |  |  |

| D    |            | 7.00        |      |                       | 0.275  |        |  |  |

| E    |            | 7.00        |      |                       | 0.275  |        |  |  |

| е    |            | 0.50        |      |                       | 0.019  |        |  |  |

| D2   | 5.00       | 5.15        | 5.25 | 0.197                 | 0.203  | 0.206  |  |  |

| E2   | 5.00       | 5.15        | 5.25 | 0.197                 | 0.203  | 0.206  |  |  |

| К    | 0.20       |             |      | 0.008                 |        |        |  |  |

| L    | 0.30       | 0.40        | 0.50 | 0.011                 | 0.015  | 0.019  |  |  |

Table 11. QFN7x7-48L package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

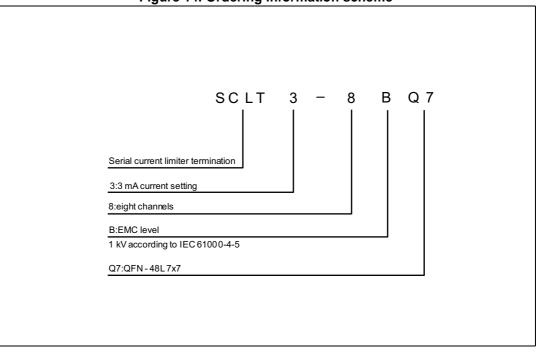

# 5 Ordering information

Figure 14. Ordering information scheme

Table 12. Ordering information

| Order code    | Marking    | Package    | Weight | Base qty | Delivery mode |

|---------------|------------|------------|--------|----------|---------------|

| SCLT3-8BQ7-TR | SCLT3-8BQ7 | QFN7x7-48L | 114 mg | 2500     | Tape and reel |

# 6 Revision history

#### Table 13. Document revision history

| Date         | Revision | Changes          |

|--------------|----------|------------------|

| 29-July-2015 | 1        | Initial release. |

| 12-Nov-2015  | 2        | Updated Table 4. |

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved